Компьютеры классические и нейронные идут близко, но всё-таки порознь. И мы, согласитесь, к такому разделению не просто привыкли, а и считаем естественным — ибо в первую очередь у них разные области применения. Классическая архитектура берёт на себя рутину механического перемалывания цифр, тогда как искусственные нейросети занимаются распознаванием образов в сравнительно редких пока особых случаях. Смычка, вероятно, когда-нибудь произойдёт, но когда и где она случится — кто способен предсказать?

Вот почему так интересно было наткнуться в новостях на упоминание именно такого примера. И не где-нибудь в лабораториях, а в чипе, который производится миллионными тиражами — конкретно, в микропроцессоре Samsung для смартфонов Galaxy S7 и Note 7. Сенсации там никакой нет, Samsung скорее всего даже не первая, кто на подобное решился, но это не делает менее волнующим ответ на вопрос: для чего обычному процессору нейроны?

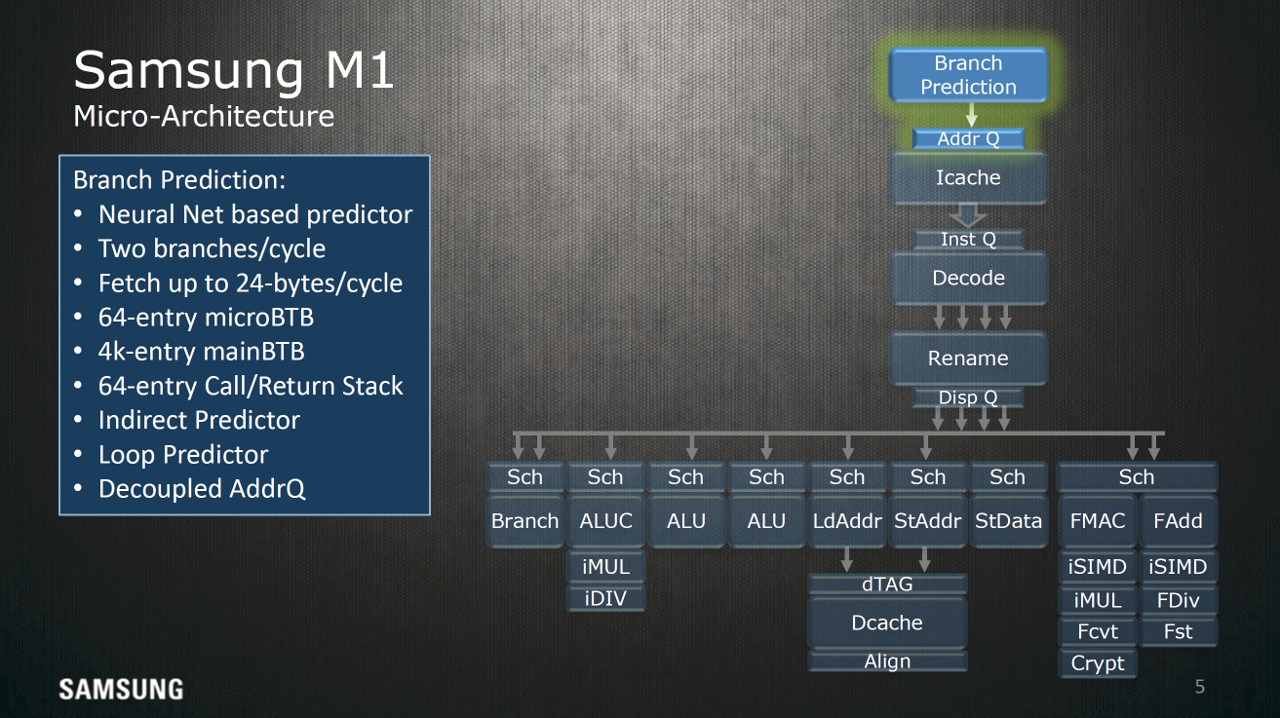

Микропроцессор, о котором идёт речь, это восьмиядерная система-на-чипе (SoC) Exynos 8890. Там три стандартных ядра ARM Cortex-A53, одно графическое, а оставшиеся четыре как раз и представляют особый интерес: они тоже ARM-производные (ARM v8), но Samsung многое и сильно в них поменяла, потратив на это три года и фактически создав собственную микроархитектуру, названную Exynos M1. Это мобильная энергоэкономичная суперскалярная многоконвейерная архитектура, но не этим она уникальна. Уникальной среди собратьев её делает блок предсказания ветвлений, основанный на искусственной нейросети.

Здесь, однако, совершенно необходимо отвлечься и сделать экскурс в историю и устройство вычислительной техники. Оставляя за кадром экспериментальные малосерийные конструкции, эволюцию массовых CPU в общем можно представить как не только погоню за миниатюризацией и тактовой частотой, но и как наращивание «интеллектуальной» мощи процессора для предсказания порядка исполнения инструкций.

8-битные микропроцессоры были тривиальными — вот, кстати, замечательный симулятор, который прямо в браузере позволяет по шагам изучить работу чипа, наподобие суперпопулярного в 8-битном мире Intel 8080. Такой процессор работает механически, тупо, почти как приснопамятная машина Тьюринга: вот он выбирает очередную инструкцию из оперативной памяти, вот её исполняет, записывает результат, вот инкрементирует программный счётчик на единицу и повторяет процесс. Сегодня кажется невероятным и смешным, что подобное когда-то вообще могло применяться для решения серьёзных задач. Но лично я первые свои деньги заработал программированием именно таких машин, да и среди вас наверняка найдутся те, кто ещё не забыл восьмибитный ассемблер.

Но уже в 90-х всё стало иначе. Микропроцессоры наделили «конвейером», и не одним, и научили выполнять инструкции не по порядку. Я, конечно, сильно упрощу и скомкаю, но суть в следующем. Вместо того, чтобы дожидаться окончания выполнения текущей команды, процессор загружал в конвейер несколько следующих инструкций по ходу действия и выполнял их одновременно — ну или по крайней мере старался выполнить, если их работа не зависела от результатов предыдущих действий (здорово помогает разбивка CISC-команда на более мелкие RISC-составляющие, что на PC впервые было реализовано в Pentium Pro). Это суперскаляр: так за один машинный цикл (или даже такт) можно было выполнить несколько команд.

А по мере того, как конвейер удлинялся, стало необходимым научиться предполагать результат условных переходов. Такое исполнение назвали спекулятивным — в том смысле, что когда процессор натыкался на команду условного перехода, то «спекулировал», то есть предсказывал, нужно этот переход исполнять или нет, после чего загружал в конвейер инструкции из выбранной ветки и продолжал работу. Минус очевиден: если предсказание было сделано неверно, конвейер придётся загружать инструкциями заново. И это прямо выводит нас на задачу предсказания ветвлений.

Задачу эту называют одной из важнейших для полупроводниковой техники последних двадцати лет. В условиях просматривающегося тупика миниатюризации, это не преувеличение: научившись предсказывать результат условных переходов максимально эффективно («с минимальным штрафом») можно существенно повысить производительность исчерпавшего прочие ресурсы процессора.

Вплоть до нулевых годов тут применялись два подхода. Первый и самый грубый: статические методы предсказания. Попросту, делается какое-то предположение относительно срабатывания того или иного условного перехода — причём, что важно, предположение это не зависит от предыдущих результатов прогона данного куска или вообще программы. Недалеко ушли от них и методы динамические или, как правильней было бы их назвать, статистические. Тут уже предположение делается на основе предыдущих результатов исполнения: грубо говоря, чем чаще переход срабатывал в прошлом, тем чаще предсказатель ветвлений будет предполагать его срабатывание в будущем. Несмотря на примитивность, оба метода работают на удивление хорошо, давая около 90% правильных предсказаний. Но настал день, когда и этого стало недостаточно. К счастью, решение уже было предложено учёными. Да, применить искусственную нейросеть!

Тут, правда, мы ступаем на землю если не неисследованную, то малоизвестную. Проблема, во-первых, в том, что сама тема ещё сравнительна юна: первые теоретические работы по нейронным предикторам ветвления относятся к началу нулевых. А во-вторых, производители не горят желанием раскрывать секреты лично своих конструкций — и даже Samsung, удивившая всех признанием (а рассказала она об этом на пресс-конференции, и даже дала кое-какие иллюстративные материалы), не исключение, потому что рассказала только в общих чертах.

Сама идея простая. Вместо грубого статистического предсказания, поставить многослойную нейросеть (хорошо подходит, в частности, классический перцептрон, который эффективно реализуется на полупроводниках), которая станет учиться и предсказывать ветвление кода. Выигрышей предполагается два. Прежде всего, уже первые теоретические изыскания показали, что нейронный предиктор может быть как минимум столь же эффективным, как и статистический. И потом, ресурсы, им занимаемые (память и время), растут с увеличением выполненного кода не экспоненциально, как у простых предсказателей, а только линейно. И их, конечно, стали применять.

Вот только примеров я, увы, дать не смогу. Даже в свежайшем и подробнейшем описании микроархитектур различных процессоров, детали нейронных блоков отсутствуют. Известно лишь, что их теперь применяет Samsung, что AMD поставила такой блок в Zen, что Intel подозревается в использовании нейронов в своих чипах. Но и только. Всё остальное — секрет! Из опыта (опять-таки больше теоретического) ясно, что большой проблемой должна стать или уже стала сравнительная медлительность нейроструктур по сравнению с грубо-механическими предсказателями — и ведётся поиск обходных путей; к счастью, по искусственным нейросетям вообще накоплен большой практический материал.

Из всего этого следует, что если теперь кто-то раскошелится на последние смартфоны Samsung, то сможет с полным правом заявлять, что в кармане у него лежит нейрокомпьютер, ну или по крайней мере компьютер, построенный с применением заимствованных у Природы структур. Но это скорее забавы ради. Интересней попробовать предположить, куда приведёт нас выбранная дорожка. Не возвещает ли появление нейроблока внутри классических микропроцессоров потерю классической архитектурой очередного значительного куска рынка? Ведь отняли же графические сопроцессоры область параллельных вычислений!

Конечно, нейронный предиктор ветвлений не применишь для решения повседневных задач. Это узкоспециализированная схематика, спрятанная у самого «сердца» чипа, чтобы минимизировать задержки. Но лиха беда начало: начнём с ветвлений, а там уже проглядывает и нейросопроцессор!

P.S. В статье использованы графические работы Pauli Rautakorpi, Intel.